- 您现在的位置:买卖IC网 > Sheet目录329 > IDT70V25L55G (IDT, Integrated Device Technology Inc)IC SRAM 128KBIT 55NS 84PGA

IDT70V35/34S/L (IDT70V25/24S/L)

High-Speed 3.3V 8/4K x 18 (8/4K x 16) Dual-Port Static RAM

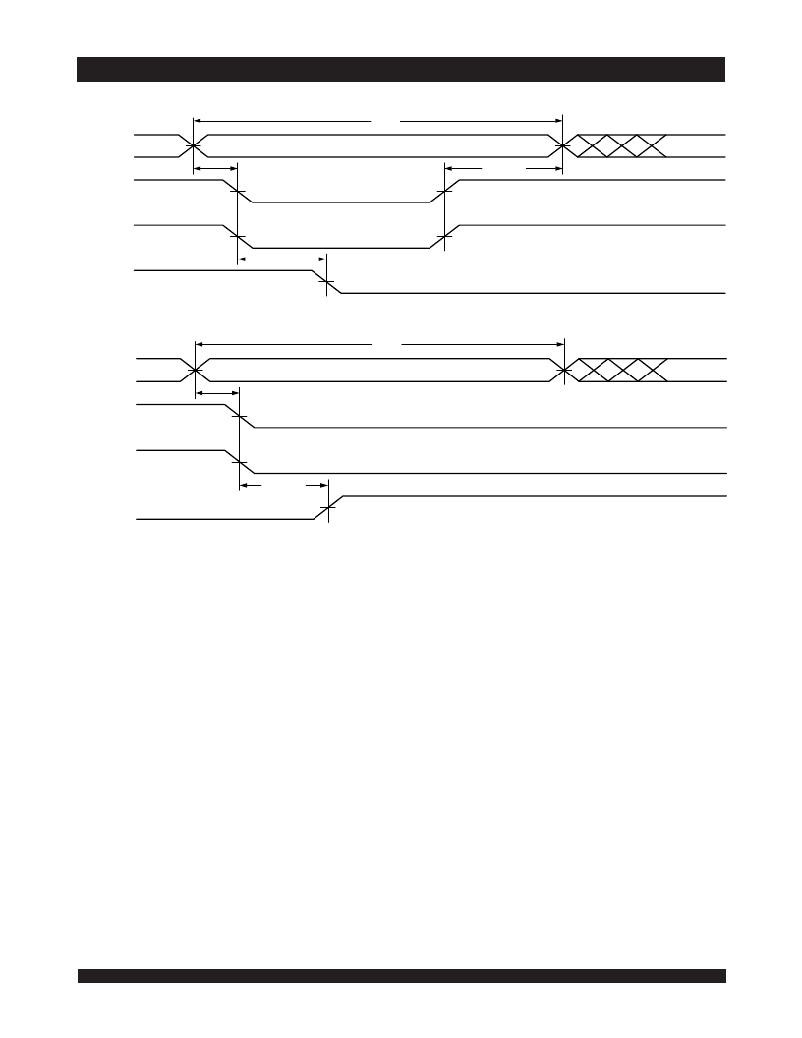

Waveform of Interrupt Timing (1)

t WC

Industrial and Commercial Temperature Ranges

ADDR "A"

INTERRUPT SET ADDRESS

(2)

(3)

t AS

t WR

(4)

CE "A"

R/ W "A"

t INS (3)

INT "B"

5624 drw 17

t RC

ADDR "B"

CE "B"

OE "B"

t AS (3)

t INR

(3)

INTERRUPT CLEAR ADDRESS

(2)

I NT "B"

5624 drw 18

NOTES:

1. All timing is the same for left and right ports. Port “A” may be either the left or right port. Port “B” is the port opposite from “A”.

2. See Interrupt Flag Truth Table III.

3. Timing depends on which enable signal ( CE or R/ W ) is asserted last.

4. Timing depends on which enable signal ( CE or R/ W ) is de-asserted first.

20

6.42

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT70V261L25PFGI

IC SRAM 256KBIT 25NS 100TQFP

IDT70V26L35G

IC SRAM 256KBIT 35NS 84PGA

IDT70V27S15PF

IC SRAM 512KBIT 15NS 100TQFP

IDT70V28L20PFGI

IC SRAM 1MBIT 20NS 100TQFP

IDT70V3319S166PRFG

IC SRAM 4MBIT 166MHZ 128TQFP

IDT70V3379S5PRFI

IC SRAM 576KBIT 5NS 128TQFP

IDT70V3389S5PRFI

IC SRAM 1.125MBIT 5NS 128TQFP

IDT70V3569S5DRI

IC SRAM 576KBIT 5NS 208QFP

相关代理商/技术参数

IDT70V25L55J

功能描述:IC SRAM 128KBIT 55NS 84PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF

IDT70V25L55J8

功能描述:IC SRAM 128KBIT 55NS 84PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF

IDT70V25L55PF

功能描述:IC SRAM 128KBIT 55NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF

IDT70V25L55PF8

功能描述:IC SRAM 128KBIT 55NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF

IDT70V25S15J

功能描述:IC SRAM 128KBIT 15NS 84PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8

IDT70V25S15J8

功能描述:IC SRAM 128KBIT 15NS 84PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF

IDT70V25S15PF

功能描述:IC SRAM 128KBIT 15NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF

IDT70V25S15PF8

功能描述:IC SRAM 128KBIT 15NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF